So today has been exceptional! I’ve made loads of progress with thanks to the arrival of my new components. As was stated previously, there were way too many losses in the gate shift registers using the 4x 1k resistor arrays. Therefore, I needed to replace the arrays for 1k resistors to the gate (maximum output current drive capability). The only resistors that actually fitted int he space of the 1206 resistor array were 0402 (gasp) so I had to wait for these to arrive – which was today! This was the first time I’d ever soldered 0402 (excluding in my project where some caps were accidentally 0402) so it was a little tense but all went well!

Performance

All of this was obviously for my new controller board which is now working! 12 motor drivers in the space of a 5x10cm PCB, I’m pretty impressed. There are however a few issues which are acceptable for this revision but will need to be addressed in the next. The worst of these issues is the shoot-through. Shoot-through is normally avoided in power inverters by introducing dead-time between turn on and off to reduce cross conduction. If the gate voltage could be changed instantly, this wouldn’t be required as the output MOSFETs would never both be in linear mode. It is this dual linear mode operation which causes a massive spike of current to flow through the MOSFETs. In this implementation however, there is no dead time and the gates are driven relatively slowly meaning shoot through is pretty intense.

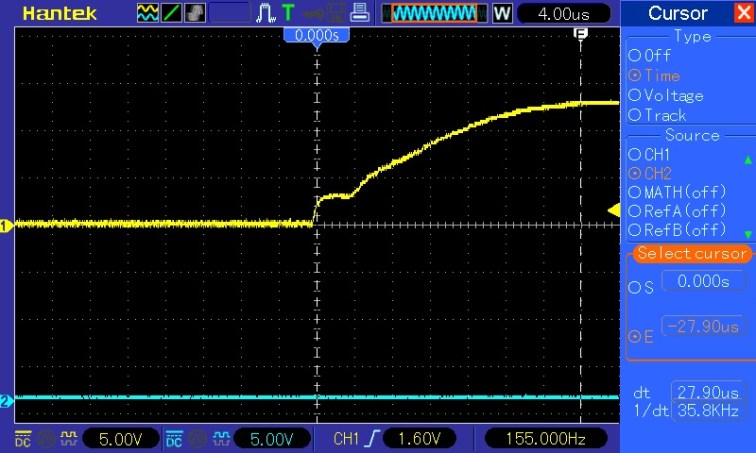

Gate rise time – ~28us! note the miller plateau oooh

Gate rise time – ~28us! note the miller plateau oooh

28us is a pretty slow rise time and is obviously due to the low gate current supplied by the 1k resistor and reasonably high gate capacitance. This means until the PMOS is turned off and the NMOS is turned fully on, current will flow from V+ to GND. This is the main power consumer for CMOS logic circuits but shouldn’t really be present in power circuits as the current levels are way higher. To put this into perspective, the current spike is so much, it causes the ceramic capacitors to buzz due to piezo effects! I also included an electrolytic capacitor in parallel with the supply too. This high ripple current however causes this electrolytic to get really warm! Along with noise and heat, the ripple current causes massive voltage dips and overshoot on both the pre-regulator and post-regulator levels.

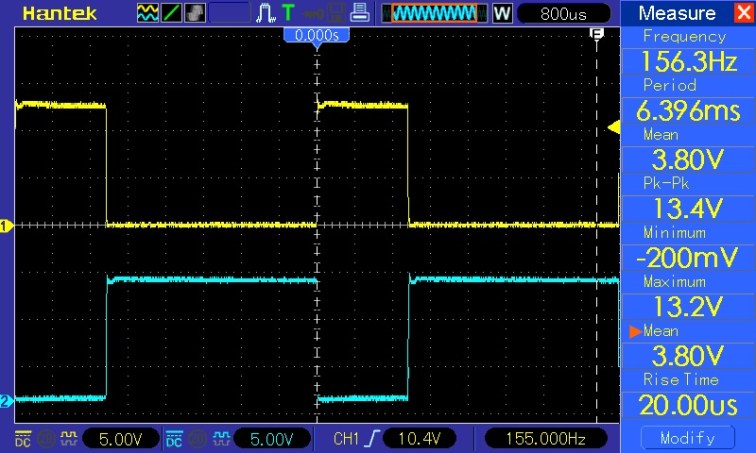

3V overshoot on the left and 12V dips on the right, MASSIVE dips.

On the plus side, we still get some pretty clean edges on the MOSFET outputs!

Complementary PWM output from the MOSFETs

Complementary PWM output from the MOSFETs

PWM Staggering

One advantage of software PWM is the ability to change the relative phase of each output. I had the idea that staggering every PWM output by 1 PWM bit (1/32th of a cycle) would reduce the supply current spikes as all devices wouldn’t be spiking at the same time. This reduced losses in the MOSFETs but seemed to increase losses in the shift registers, I think this is because instead of switching all MOSFET gates at the same time, the outputs are continuously switched throughout the cycle. This means more “effective” switches per cycle, increasing switching losses.

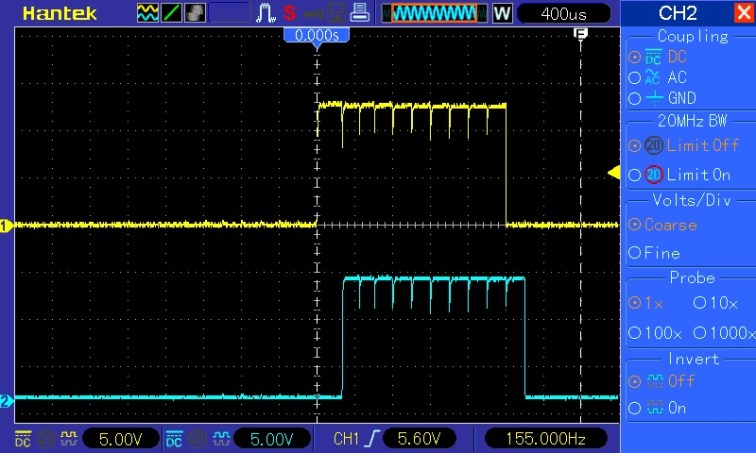

Looking at output 1a and 2a, note the staggered phase though there are spikes where every other output switches

Looking at output 1a and 2a, note the staggered phase though there are spikes where every other output switches

As can be seen above, staggering the PWM maintains the PWM duty cycle but moves its position in time.

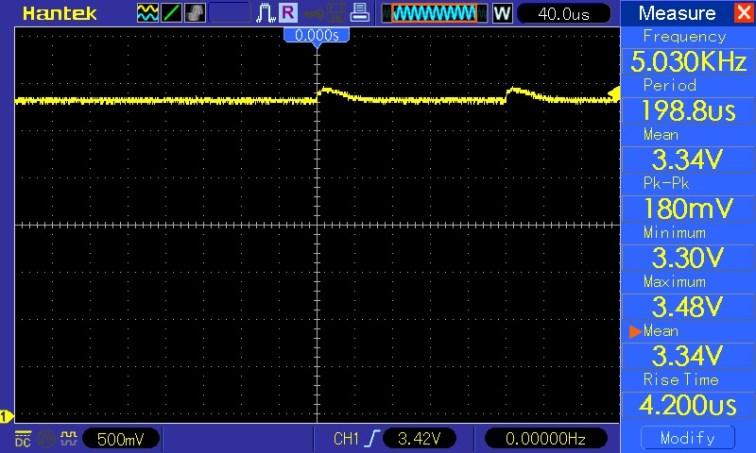

3.3V overshoot with staggered PWM

3.3V overshoot with staggered PWM

Introducing staggered PWM reduces the overshoot present on the 3.3V regulator output obviously indicating a reduction in voltage dip.

Half PWM staggering

Obviously having large losses in the output shift registers isn’t ideal so the middle ground for fixing this would be to change the amount of staggering. Instead of staggering every PWM output, the phase only changes after every 2 outputs meaning outputs 1 and 2 are in phase, 3 and 4 are in phase but time delayed from 1 and 2, and so on. This seemed a pleasant middle ground but increased capacitor noise.

Half staggered PWM outputs showing fewer voltage dips.

Shoot-through

This shoot-through is definitely bad increasing losses in the switches as well as producing audible noise and supply issues. Another problem however which is a little less obviously is the EMI from these massive current spikes! I’ve never had an EMI problem before but having such a large dI/dt produces induced currents in loads of different areas of the circuit. The most affected of these areas is the ST-link dongle which sometimes just cuts out due to induced EMI. It is therefore vital that this issue is fixed in the next revision.

Solution

I was looking around the internet at solutions that meant I could keep the same kind of circuitry with the addition of minimal components (i.e. not including dedicated gate drivers – costly components!). I saw a post on edaboard (normally regarded as poor quality but hey) where someone mentions adding additional gate resistance to induce a delay and slow the turn on and turn off of the two MOSFETs. This obviously makes sense so I gate it a simulation and it seems really sound! It needs two gate resistors per MOSFET (not major) along with a dual SOT23 diode. The idea behind is that you want to slow the turn on of the upper PMOS and slow the turn off of the lower NMOS. This is done by using a large gate resistor with a small gate resistor in parallel with a series diode (confusing, I know). The direction of the diode depicts which edge is slowed. Using the inherent capacitance of the gate means that this resistor value can be varied to set the turn off/on time.

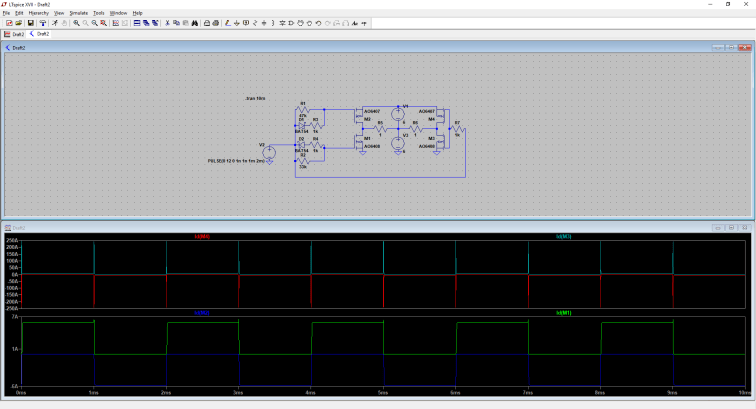

Simulating this in LTSpice with a complementary MOSFET pair proved successful too. Inclusion of shoot-through prevention drive

Inclusion of shoot-through prevention drive

As can be seen in the above picture, the green and blue traces are the current through the left side half bridge with the shoot-through prevention. The red and light blue traces are for the right side half bridge which is configured as an inverter driven by a 1k resistor. The simulation shows 200A current spikes as the shoot-through current, gah!

This small addition will be integrated into the next PCB if I get round to it. I will be using this one however for the near future.

Movement

In the video, I show the hexapod moving its legs in a circular fashion. This movement is generated by setting the PID demands to phase shifted sine waves. By varying the sine wave amplitude, the eccentricity of the ellipse can be changed, this means for fastest movement, I can only lift the leg a bit for maximum ground contact. I hadn’t previously thought of controlling the legs like this so I’ll be using this for my remote control test!

With regards to the leg phases, on a single side, the front-most leg is set to phase 0, the middle leg is then 120 degrees ahead of the front leg and the rear leg is 120 degrees ahead of that. This 3 phase motion should produce a nice smooth movement – like how torque ripple is reduced in a 3 phase AC motor! The legs on the opposite side are merely 180 degrees out of phase with the first side. Its worth noting that if the front and back legs are in phase and the middle leg is 180 degrees out of phase, the hexapod will walk using a tripod-esque smooth gait.

I’ve gotta wait for a few more components to arrive (ugh wire) but once they do, I can look to testing it!

Keep tuned…..